Forums » Req. WJ2(Zynq-7000) support »

Cannot build hardware for i2c_demo

Cannot build hardware for i2c_demo

Added by Johan Henning about 3 years ago

1. When executing the .tcl file a message is displayed that it cannot find the .xdc file. It seems that the .xdc file shall be moved two directories up

2. When executing the .tcl file (after moving the .xdc file) this message pops up: WARNING: [Vivado 12-9135] Ignoring repo path (C:/Users/admin/AppData/Roaming/Xilinx/Vivado/2020.2/xhub/board_store/xilinx_board_store) because it contains no board files

No block design is created.

Replies (6)

RE: Cannot build hardware for i2c_demo

-

Added by Shawn Sebastian Pulle (ฌอน) about 3 years ago

RE: Cannot build hardware for i2c_demo

-

Added by Shawn Sebastian Pulle (ฌอน) about 3 years ago

Hi Johan,

Thank you for the feedback. These changes to the tcl file will be implemented in a future release.

It is strange that no block design is being created with the second warning. In our testing it did not stop the block design.

RE: Cannot build hardware for i2c_demo

-

Added by Johan Henning about 3 years ago

RE: Cannot build hardware for i2c_demo

-

Added by Johan Henning about 3 years ago

Hello,

See below my logfiles. It might be a good idea that Aimagin creates a build / test PC with a clean installation of Vivado and the required board files to verify that the delivered software will work at their customers site.

This is the logfile when trying to build the hardware:

start_guicd C:/AimaginProjects/Zybo/Hardware_Z7000/i2c_demo

source i2c_demo.tcl

- proc checkRequiredFiles { origin_dir} {

- set status true

- set files [list \

- "C:/Aimagin/zynq7000_xilinx/Other-Board_Files/zyboz7_project/vivado/My_Zybo-Z7-Master.xdc" \

- ]

- foreach ifile $files {

- if { ![file isfile $ifile] } {

- puts " Could not find remote file $ifile "

- set status false

- }

- }

- return $status

- }

- set origin_dir "."

- if { [info exists ::origin_dir_loc] } {

- set origin_dir $::origin_dir_loc

- }

- set xil_proj_name "project_1"

- if { [info exists ::user_project_name] } {

- set xil_proj_name $::user_project_name

- }

- variable script_file

- set script_file "i2c_demo.tcl"

- proc print_help {} {

- variable script_file

- puts "\nDescription:"

- puts "Recreate a Vivado project from this script. The created project will be"

- puts "functionally equivalent to the original project for which this script was"

- puts "generated. The script contains commands for creating a project, filesets,"

- puts "runs, adding/importing sources and setting properties on various objects.\n"

- puts "Syntax:"

- puts "$script_file"

- puts "$script_file -tclargs \[--origin_dir <path>\]"

- puts "$script_file -tclargs \[--project_name <name>\]"

- puts "$script_file -tclargs \[--help\]\n"

- puts "Usage:"

- puts "Name Description"

- puts "-------------------------------------------------------------------------"

- puts "\[--origin_dir <path>\] Determine source file paths wrt this path. Default"

- puts " origin_dir path value is \".\", otherwise, the value"

- puts " that was set with the \"-paths_relative_to\" switch"

- puts " when this script was generated.\n"

- puts "\[--project_name <name>\] Create project with the specified name. Default"

- puts " name is the name of the project from where this"

- puts " script was generated.\n"

- puts "\[--help\] Print help information for this script"

- puts "-------------------------------------------------------------------------\n"

- exit 0

- }

- if { $::argc > 0 } {

- for {set i 0} {$i < $::argc} {incr i} {

- set option [string trim [lindex $::argv $i]]

- switch

regexp -$option { - "--origin_dir" { incr i; set origin_dir [lindex $::argv $i] }

- "--project_name" { incr i; set xil_proj_name [lindex $::argv $i] }

- "--help" { print_help }

- default {

- if { [regexp {^-} $option] } {

- puts "ERROR: Unknown option '$option' specified, please type '$script_file -tclargs --help' for usage info.\n"

- return 1

- }

- }

- }

- }

- }

- set orig_proj_dir "[file normalize "$origin_dir/project_1"]"

- set validate_required 0

- if { $validate_required } {

- if { [checkRequiredFiles $origin_dir] } {

- puts "Tcl file $script_file is valid. All files required for project creation is accesable. "

- } else {

- puts "Tcl file $script_file is not valid. Not all files required for project creation is accesable. "

- return

- }

- }

- create_project ${_xil_proj_name_} ./${_xil_proj_name_} -part xc7z020clg400-1

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'C:/Xilinx/Vivado/2020.2/data/ip'.

create_project: Time (s): cpu = 00:00:04 ; elapsed = 00:00:08 . Memory (MB): peak = 1119.531 ; gain = 0.000 - set proj_dir [get_property directory [current_project]]

- set obj [current_project]

- set_property -name "board_part_repo_paths" -value "[file normalize "$origin_dir/../../../../../../Users/admin/AppData/Roaming/Xilinx/Vivado/2020.2/xhub/board_store/xilinx_board_store"]" -objects $obj

WARNING: [Vivado 12-9135] Ignoring repo path (C:/Users/admin/AppData/Roaming/Xilinx/Vivado/2020.2/xhub/board_store/xilinx_board_store) because it contains no board files - set_property -name "board_part" -value "digilentinc.com:zybo-z7-20:part0:1.0" -objects $obj

- set_property -name "default_lib" -value "xil_defaultlib" -objects $obj

- set_property -name "enable_vhdl_2008" -value "1" -objects $obj

- set_property -name "ip_cache_permissions" -value "read write" -objects $obj

- set_property -name "ip_output_repo" -value "$proj_dir/${_xil_proj_name_}.cache/ip" -objects $obj

- set_property -name "mem.enable_memory_map_generation" -value "1" -objects $obj

- set_property -name "platform.board_id" -value "zybo-z7-20" -objects $obj

- set_property -name "sim.central_dir" -value "$proj_dir/${_xil_proj_name_}.ip_user_files" -objects $obj

- set_property -name "sim.ip.auto_export_scripts" -value "1" -objects $obj

- set_property -name "simulator_language" -value "Mixed" -objects $obj

- set_property -name "target_language" -value "VHDL" -objects $obj

- if {[string equal [get_filesets -quiet sources_1] ""]} {

- create_fileset -srcset sources_1

- }

- set obj [get_filesets sources_1]

- set obj [get_filesets sources_1]

- set_property -name "top" -value "design_1_wrapper" -objects $obj

- if {[string equal [get_filesets -quiet constrs_1] ""]} {

- create_fileset -constrset constrs_1

- }

- set obj [get_filesets constrs_1]

- set file "[file normalize "$origin_dir/../My_Zybo-Z7-Master.xdc"]"

ERROR: [Vivado 12-172] File or Directory 'C:/AimaginProjects/Zybo/Hardware_Z7000/My_Zybo-Z7-Master.xdc' does not exist

After copying the file My_Zybo-Z7-Master.xdc to a location two levels up in the directory tree this is the result (no block design is created):

source i2c_demo.tcl- proc checkRequiredFiles { origin_dir} {

- set status true

- set files [list \

- "C:/Aimagin/zynq7000_xilinx/Other-Board_Files/zyboz7_project/vivado/My_Zybo-Z7-Master.xdc" \

- ]

- foreach ifile $files {

- if { ![file isfile $ifile] } {

- puts " Could not find remote file $ifile "

- set status false

- }

- }

- return $status

- }

- set origin_dir "."

- if { [info exists ::origin_dir_loc] } {

- set origin_dir $::origin_dir_loc

- }

- set xil_proj_name "project_1"

- if { [info exists ::user_project_name] } {

- set xil_proj_name $::user_project_name

- }

- variable script_file

- set script_file "i2c_demo.tcl"

- proc print_help {} {

- variable script_file

- puts "\nDescription:"

- puts "Recreate a Vivado project from this script. The created project will be"

- puts "functionally equivalent to the original project for which this script was"

- puts "generated. The script contains commands for creating a project, filesets,"

- puts "runs, adding/importing sources and setting properties on various objects.\n"

- puts "Syntax:"

- puts "$script_file"

- puts "$script_file -tclargs \[--origin_dir <path>\]"

- puts "$script_file -tclargs \[--project_name <name>\]"

- puts "$script_file -tclargs \[--help\]\n"

- puts "Usage:"

- puts "Name Description"

- puts "-------------------------------------------------------------------------"

- puts "\[--origin_dir <path>\] Determine source file paths wrt this path. Default"

- puts " origin_dir path value is \".\", otherwise, the value"

- puts " that was set with the \"-paths_relative_to\" switch"

- puts " when this script was generated.\n"

- puts "\[--project_name <name>\] Create project with the specified name. Default"

- puts " name is the name of the project from where this"

- puts " script was generated.\n"

- puts "\[--help\] Print help information for this script"

- puts "-------------------------------------------------------------------------\n"

- exit 0

- }

- if { $::argc > 0 } {

- for {set i 0} {$i < $::argc} {incr i} {

- set option [string trim [lindex $::argv $i]]

- switch

regexp -$option { - "--origin_dir" { incr i; set origin_dir [lindex $::argv $i] }

- "--project_name" { incr i; set xil_proj_name [lindex $::argv $i] }

- "--help" { print_help }

- default {

- if { [regexp {^-} $option] } {

- puts "ERROR: Unknown option '$option' specified, please type '$script_file -tclargs --help' for usage info.\n"

- return 1

- }

- }

- }

- }

- }

- set orig_proj_dir "[file normalize "$origin_dir/project_1"]"

- set validate_required 0

- if { $validate_required } {

- if { [checkRequiredFiles $origin_dir] } {

- puts "Tcl file $script_file is valid. All files required for project creation is accesable. "

- } else {

- puts "Tcl file $script_file is not valid. Not all files required for project creation is accesable. "

- return

- }

- }

- create_project ${_xil_proj_name_} ./${_xil_proj_name_} -part xc7z020clg400-1

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'C:/Xilinx/Vivado/2020.2/data/ip'. - set proj_dir [get_property directory [current_project]]

- set obj [current_project]

- set_property -name "board_part_repo_paths" -value "[file normalize "$origin_dir/../../../../../../Users/admin/AppData/Roaming/Xilinx/Vivado/2020.2/xhub/board_store/xilinx_board_store"]" -objects $obj

WARNING: [Vivado 12-9135] Ignoring repo path (C:/Users/admin/AppData/Roaming/Xilinx/Vivado/2020.2/xhub/board_store/xilinx_board_store) because it contains no board files - set_property -name "board_part" -value "digilentinc.com:zybo-z7-20:part0:1.0" -objects $obj

- set_property -name "default_lib" -value "xil_defaultlib" -objects $obj

- set_property -name "enable_vhdl_2008" -value "1" -objects $obj

- set_property -name "ip_cache_permissions" -value "read write" -objects $obj

- set_property -name "ip_output_repo" -value "$proj_dir/${_xil_proj_name_}.cache/ip" -objects $obj

- set_property -name "mem.enable_memory_map_generation" -value "1" -objects $obj

- set_property -name "platform.board_id" -value "zybo-z7-20" -objects $obj

- set_property -name "sim.central_dir" -value "$proj_dir/${_xil_proj_name_}.ip_user_files" -objects $obj

- set_property -name "sim.ip.auto_export_scripts" -value "1" -objects $obj

- set_property -name "simulator_language" -value "Mixed" -objects $obj

- set_property -name "target_language" -value "VHDL" -objects $obj

- if {[string equal [get_filesets -quiet sources_1] ""]} {

- create_fileset -srcset sources_1

- }

- set obj [get_filesets sources_1]

- set obj [get_filesets sources_1]

- set_property -name "top" -value "design_1_wrapper" -objects $obj

- if {[string equal [get_filesets -quiet constrs_1] ""]} {

- create_fileset -constrset constrs_1

- }

- set obj [get_filesets constrs_1]

- set file "[file normalize "$origin_dir/../My_Zybo-Z7-Master.xdc"]"

- set file_added [add_files -norecurse -fileset $obj [list $file]]

- set file "$origin_dir/../My_Zybo-Z7-Master.xdc"

- set file [file normalize $file]

- set file_obj [get_files -of_objects [get_filesets constrs_1] [list "*$file"]]

- set_property -name "file_type" -value "XDC" -objects $file_obj

- set obj [get_filesets constrs_1]

- if {[string equal [get_filesets -quiet sim_1] ""]} {

- create_fileset -simset sim_1

- }

- set obj [get_filesets sim_1]

- set obj [get_filesets sim_1]

- set_property -name "hbs.configure_design_for_hier_access" -value "1" -objects $obj

- set_property -name "top" -value "design_1_wrapper" -objects $obj

- set_property -name "top_lib" -value "xil_defaultlib" -objects $obj

- set obj [get_filesets utils_1]

- set obj [get_filesets utils_1]

- proc cr_bd_design_1 { parentCell } {

- # CHANGE DESIGN NAME HERE

- set design_name design_1

- common::send_gid_msg -ssname BD::TCL -id 2010 -severity "INFO" "Currently there is no design <$design_name> in project, so creating one..."

- create_bd_design $design_name

- set bCheckIPsPassed 1

- ##################################################################

- # CHECK IPs

- ##################################################################

- set bCheckIPs 1

- if { $bCheckIPs == 1 } {

- set list_check_ips "\

- xilinx.com:ip:processing_system7:5.5\

- "

- set list_ips_missing ""

- common::send_gid_msg -ssname BD::TCL -id 2011 -severity "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."

- foreach ip_vlnv $list_check_ips {

- set ip_obj [get_ipdefs -all $ip_vlnv]

- if { $ip_obj eq "" } {

- lappend list_ips_missing $ip_vlnv

- }

- }

- if { $list_ips_missing ne "" } {

- catch {common::send_gid_msg -ssname BD::TCL -id 2012 -severity "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP to the project." }

- set bCheckIPsPassed 0

- }

- }

- if { $bCheckIPsPassed != 1 } {

- common::send_gid_msg -ssname BD::TCL -id 2023 -severity "WARNING" "Will not continue with creation of design due to the error(s) above."

- return 3

- }

- variable script_folder

- if { $parentCell eq "" } {

- set parentCell [get_bd_cells /]

- }

- # Get object for parentCell

- set parentObj [get_bd_cells $parentCell]

- if { $parentObj == "" } {

- catch {common::send_gid_msg -ssname BD::TCL -id 2090 -severity "ERROR" "Unable to find parent cell <$parentCell>!"}

- return

- }

- # Make sure parentObj is hier blk

- set parentType [get_property TYPE $parentObj]

- if { $parentType ne "hier" } {

- catch {common::send_gid_msg -ssname BD::TCL -id 2091 -severity "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

- return

- }

- # Save current instance; Restore later

- set oldCurInst [current_bd_instance .]

- # Set parent object as current

- current_bd_instance $parentObj

- # Create interface ports

- set DDR [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:ddrx_rtl:1.0 DDR ]

- set FIXED_IO [ create_bd_intf_port -mode Master -vlnv xilinx.com:display_processing_system7:fixedio_rtl:1.0 FIXED_IO ]

- set GPIO_0_0 [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:gpio_rtl:1.0 GPIO_0_0 ]

- # Create ports

- # Create instance: processing_system7_0, and set properties

- set processing_system7_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:processing_system7:5.5 processing_system7_0 ]

- set_property -dict [ list \

- CONFIG.PCW_ACT_APU_PERIPHERAL_FREQMHZ {666.666687} \

- CONFIG.PCW_ACT_CAN_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_DCI_PERIPHERAL_FREQMHZ {10.158730} \

- CONFIG.PCW_ACT_ENET0_PERIPHERAL_FREQMHZ {125.000000} \

- CONFIG.PCW_ACT_ENET1_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_FPGA0_PERIPHERAL_FREQMHZ {50.000000} \

- CONFIG.PCW_ACT_FPGA1_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_FPGA2_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_FPGA3_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_PCAP_PERIPHERAL_FREQMHZ {200.000000} \

- CONFIG.PCW_ACT_QSPI_PERIPHERAL_FREQMHZ {200.000000} \

- CONFIG.PCW_ACT_SDIO_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_SMC_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_SPI_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_TPIU_PERIPHERAL_FREQMHZ {200.000000} \

- CONFIG.PCW_ACT_TTC0_CLK0_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC0_CLK1_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC0_CLK2_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC1_CLK0_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC1_CLK1_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC1_CLK2_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_UART_PERIPHERAL_FREQMHZ {100.000000} \

- CONFIG.PCW_ACT_WDT_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_APU_CLK_RATIO_ENABLE {6:2:1} \

- CONFIG.PCW_APU_PERIPHERAL_FREQMHZ {667} \

- CONFIG.PCW_ARMPLL_CTRL_FBDIV {40} \

- CONFIG.PCW_CAN_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_CAN_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_CLK0_FREQ {50000000} \

- CONFIG.PCW_CLK1_FREQ {10000000} \

- CONFIG.PCW_CLK2_FREQ {10000000} \

- CONFIG.PCW_CLK3_FREQ {10000000} \

- CONFIG.PCW_CPU_CPU_6X4X_MAX_RANGE {667} \

- CONFIG.PCW_CPU_CPU_PLL_FREQMHZ {1333.333} \

- CONFIG.PCW_CPU_PERIPHERAL_CLKSRC {ARM PLL} \

- CONFIG.PCW_CPU_PERIPHERAL_DIVISOR0 {2} \

- CONFIG.PCW_CRYSTAL_PERIPHERAL_FREQMHZ {33.333333} \

- CONFIG.PCW_DCI_PERIPHERAL_CLKSRC {DDR PLL} \

- CONFIG.PCW_DCI_PERIPHERAL_DIVISOR0 {15} \

- CONFIG.PCW_DCI_PERIPHERAL_DIVISOR1 {7} \

- CONFIG.PCW_DCI_PERIPHERAL_FREQMHZ {10.159} \

- CONFIG.PCW_DDRPLL_CTRL_FBDIV {32} \

- CONFIG.PCW_DDR_DDR_PLL_FREQMHZ {1066.667} \

- CONFIG.PCW_DDR_HPRLPR_QUEUE_PARTITION {HPR/LPR} \

- CONFIG.PCW_DDR_HPR_TO_CRITICAL_PRIORITY_LEVEL {15} \

- CONFIG.PCW_DDR_LPR_TO_CRITICAL_PRIORITY_LEVEL {2} \

- CONFIG.PCW_DDR_PERIPHERAL_CLKSRC {DDR PLL} \

- CONFIG.PCW_DDR_PERIPHERAL_DIVISOR0 {2} \

- CONFIG.PCW_DDR_PORT0_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_PORT1_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_PORT2_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_PORT3_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_RAM_HIGHADDR {0x3FFFFFFF} \

- CONFIG.PCW_DDR_WRITE_TO_CRITICAL_PRIORITY_LEVEL {2} \

- CONFIG.PCW_ENET0_ENET0_IO {MIO 16 .. 27} \

- CONFIG.PCW_ENET0_GRP_MDIO_ENABLE {1} \

- CONFIG.PCW_ENET0_GRP_MDIO_IO {MIO 52 .. 53} \

- CONFIG.PCW_ENET0_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_ENET0_PERIPHERAL_DIVISOR0 {8} \

- CONFIG.PCW_ENET0_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_ENET0_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_ENET0_PERIPHERAL_FREQMHZ {1000 Mbps} \

- CONFIG.PCW_ENET0_RESET_ENABLE {0} \

- CONFIG.PCW_ENET1_GRP_MDIO_ENABLE {0} \

- CONFIG.PCW_ENET1_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_ENET1_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_ENET1_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_ENET1_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_ENET1_PERIPHERAL_FREQMHZ {1000 Mbps} \

- CONFIG.PCW_ENET1_RESET_ENABLE {0} \

- CONFIG.PCW_ENET_RESET_ENABLE {1} \

- CONFIG.PCW_ENET_RESET_POLARITY {Active Low} \

- CONFIG.PCW_ENET_RESET_SELECT {Share reset pin} \

- CONFIG.PCW_EN_4K_TIMER {0} \

- CONFIG.PCW_EN_EMIO_ENET0 {0} \

- CONFIG.PCW_EN_EMIO_GPIO {1} \

- CONFIG.PCW_EN_EMIO_I2C0 {0} \

- CONFIG.PCW_EN_EMIO_I2C1 {0} \

- CONFIG.PCW_EN_ENET0 {1} \

- CONFIG.PCW_EN_GPIO {1} \

- CONFIG.PCW_EN_I2C0 {1} \

- CONFIG.PCW_EN_I2C1 {1} \

- CONFIG.PCW_EN_QSPI {1} \

- CONFIG.PCW_EN_SDIO0 {0} \

- CONFIG.PCW_EN_UART1 {1} \

- CONFIG.PCW_EN_USB0 {0} \

- CONFIG.PCW_FCLK0_PERIPHERAL_DIVISOR0 {5} \

- CONFIG.PCW_FCLK0_PERIPHERAL_DIVISOR1 {4} \

- CONFIG.PCW_FCLK1_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_FCLK1_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_FCLK2_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_FCLK2_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_FCLK3_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_FCLK3_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_FPGA_FCLK0_ENABLE {1} \

- CONFIG.PCW_FPGA_FCLK1_ENABLE {0} \

- CONFIG.PCW_FPGA_FCLK2_ENABLE {0} \

- CONFIG.PCW_FPGA_FCLK3_ENABLE {0} \

- CONFIG.PCW_GPIO_EMIO_GPIO_ENABLE {1} \

- CONFIG.PCW_GPIO_EMIO_GPIO_IO {26} \

- CONFIG.PCW_GPIO_EMIO_GPIO_WIDTH {26} \

- CONFIG.PCW_GPIO_MIO_GPIO_ENABLE {1} \

- CONFIG.PCW_GPIO_MIO_GPIO_IO {MIO} \

- CONFIG.PCW_GPIO_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_I2C0_GRP_INT_ENABLE {1} \

- CONFIG.PCW_I2C0_GRP_INT_IO {EMIO} \

- CONFIG.PCW_I2C0_I2C0_IO {MIO 14 .. 15} \

- CONFIG.PCW_I2C0_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_I2C0_RESET_ENABLE {0} \

- CONFIG.PCW_I2C1_GRP_INT_ENABLE {1} \

- CONFIG.PCW_I2C1_GRP_INT_IO {EMIO} \

- CONFIG.PCW_I2C1_I2C1_IO {MIO 12 .. 13} \

- CONFIG.PCW_I2C1_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_I2C1_RESET_ENABLE {0} \

- CONFIG.PCW_I2C_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_I2C_RESET_ENABLE {1} \

- CONFIG.PCW_I2C_RESET_SELECT {Share reset pin} \

- CONFIG.PCW_IOPLL_CTRL_FBDIV {30} \

- CONFIG.PCW_IO_IO_PLL_FREQMHZ {1000.000} \

- CONFIG.PCW_IRQ_F2P_MODE {DIRECT} \

- CONFIG.PCW_MIO_0_DIRECTION {inout} \

- CONFIG.PCW_MIO_0_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_0_PULLUP {enabled} \

- CONFIG.PCW_MIO_0_SLEW {slow} \

- CONFIG.PCW_MIO_10_DIRECTION {inout} \

- CONFIG.PCW_MIO_10_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_10_PULLUP {enabled} \

- CONFIG.PCW_MIO_10_SLEW {slow} \

- CONFIG.PCW_MIO_11_DIRECTION {inout} \

- CONFIG.PCW_MIO_11_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_11_PULLUP {enabled} \

- CONFIG.PCW_MIO_11_SLEW {slow} \

- CONFIG.PCW_MIO_12_DIRECTION {inout} \

- CONFIG.PCW_MIO_12_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_12_PULLUP {enabled} \

- CONFIG.PCW_MIO_12_SLEW {slow} \

- CONFIG.PCW_MIO_13_DIRECTION {inout} \

- CONFIG.PCW_MIO_13_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_13_PULLUP {enabled} \

- CONFIG.PCW_MIO_13_SLEW {slow} \

- CONFIG.PCW_MIO_14_DIRECTION {inout} \

- CONFIG.PCW_MIO_14_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_14_PULLUP {enabled} \

- CONFIG.PCW_MIO_14_SLEW {slow} \

- CONFIG.PCW_MIO_15_DIRECTION {inout} \

- CONFIG.PCW_MIO_15_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_15_PULLUP {enabled} \

- CONFIG.PCW_MIO_15_SLEW {slow} \

- CONFIG.PCW_MIO_16_DIRECTION {out} \

- CONFIG.PCW_MIO_16_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_16_PULLUP {enabled} \

- CONFIG.PCW_MIO_16_SLEW {fast} \

- CONFIG.PCW_MIO_17_DIRECTION {out} \

- CONFIG.PCW_MIO_17_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_17_PULLUP {enabled} \

- CONFIG.PCW_MIO_17_SLEW {fast} \

- CONFIG.PCW_MIO_18_DIRECTION {out} \

- CONFIG.PCW_MIO_18_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_18_PULLUP {enabled} \

- CONFIG.PCW_MIO_18_SLEW {fast} \

- CONFIG.PCW_MIO_19_DIRECTION {out} \

- CONFIG.PCW_MIO_19_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_19_PULLUP {enabled} \

- CONFIG.PCW_MIO_19_SLEW {fast} \

- CONFIG.PCW_MIO_1_DIRECTION {out} \

- CONFIG.PCW_MIO_1_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_1_PULLUP {enabled} \

- CONFIG.PCW_MIO_1_SLEW {slow} \

- CONFIG.PCW_MIO_20_DIRECTION {out} \

- CONFIG.PCW_MIO_20_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_20_PULLUP {enabled} \

- CONFIG.PCW_MIO_20_SLEW {fast} \

- CONFIG.PCW_MIO_21_DIRECTION {out} \

- CONFIG.PCW_MIO_21_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_21_PULLUP {enabled} \

- CONFIG.PCW_MIO_21_SLEW {fast} \

- CONFIG.PCW_MIO_22_DIRECTION {in} \

- CONFIG.PCW_MIO_22_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_22_PULLUP {enabled} \

- CONFIG.PCW_MIO_22_SLEW {fast} \

- CONFIG.PCW_MIO_23_DIRECTION {in} \

- CONFIG.PCW_MIO_23_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_23_PULLUP {enabled} \

- CONFIG.PCW_MIO_23_SLEW {fast} \

- CONFIG.PCW_MIO_24_DIRECTION {in} \

- CONFIG.PCW_MIO_24_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_24_PULLUP {enabled} \

- CONFIG.PCW_MIO_24_SLEW {fast} \

- CONFIG.PCW_MIO_25_DIRECTION {in} \

- CONFIG.PCW_MIO_25_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_25_PULLUP {enabled} \

- CONFIG.PCW_MIO_25_SLEW {fast} \

- CONFIG.PCW_MIO_26_DIRECTION {in} \

- CONFIG.PCW_MIO_26_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_26_PULLUP {enabled} \

- CONFIG.PCW_MIO_26_SLEW {fast} \

- CONFIG.PCW_MIO_27_DIRECTION {in} \

- CONFIG.PCW_MIO_27_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_27_PULLUP {enabled} \

- CONFIG.PCW_MIO_27_SLEW {fast} \

- CONFIG.PCW_MIO_28_DIRECTION {inout} \

- CONFIG.PCW_MIO_28_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_28_PULLUP {enabled} \

- CONFIG.PCW_MIO_28_SLEW {fast} \

- CONFIG.PCW_MIO_29_DIRECTION {inout} \

- CONFIG.PCW_MIO_29_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_29_PULLUP {enabled} \

- CONFIG.PCW_MIO_29_SLEW {fast} \

- CONFIG.PCW_MIO_2_DIRECTION {inout} \

- CONFIG.PCW_MIO_2_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_2_PULLUP {disabled} \

- CONFIG.PCW_MIO_2_SLEW {slow} \

- CONFIG.PCW_MIO_30_DIRECTION {inout} \

- CONFIG.PCW_MIO_30_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_30_PULLUP {enabled} \

- CONFIG.PCW_MIO_30_SLEW {fast} \

- CONFIG.PCW_MIO_31_DIRECTION {inout} \

- CONFIG.PCW_MIO_31_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_31_PULLUP {enabled} \

- CONFIG.PCW_MIO_31_SLEW {fast} \

- CONFIG.PCW_MIO_32_DIRECTION {inout} \

- CONFIG.PCW_MIO_32_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_32_PULLUP {enabled} \

- CONFIG.PCW_MIO_32_SLEW {fast} \

- CONFIG.PCW_MIO_33_DIRECTION {inout} \

- CONFIG.PCW_MIO_33_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_33_PULLUP {enabled} \

- CONFIG.PCW_MIO_33_SLEW {fast} \

- CONFIG.PCW_MIO_34_DIRECTION {inout} \

- CONFIG.PCW_MIO_34_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_34_PULLUP {enabled} \

- CONFIG.PCW_MIO_34_SLEW {fast} \

- CONFIG.PCW_MIO_35_DIRECTION {inout} \

- CONFIG.PCW_MIO_35_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_35_PULLUP {enabled} \

- CONFIG.PCW_MIO_35_SLEW {fast} \

- CONFIG.PCW_MIO_36_DIRECTION {inout} \

- CONFIG.PCW_MIO_36_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_36_PULLUP {enabled} \

- CONFIG.PCW_MIO_36_SLEW {fast} \

- CONFIG.PCW_MIO_37_DIRECTION {inout} \

- CONFIG.PCW_MIO_37_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_37_PULLUP {enabled} \

- CONFIG.PCW_MIO_37_SLEW {fast} \

- CONFIG.PCW_MIO_38_DIRECTION {inout} \

- CONFIG.PCW_MIO_38_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_38_PULLUP {enabled} \

- CONFIG.PCW_MIO_38_SLEW {fast} \

- CONFIG.PCW_MIO_39_DIRECTION {inout} \

- CONFIG.PCW_MIO_39_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_39_PULLUP {enabled} \

- CONFIG.PCW_MIO_39_SLEW {fast} \

- CONFIG.PCW_MIO_3_DIRECTION {inout} \

- CONFIG.PCW_MIO_3_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_3_PULLUP {disabled} \

- CONFIG.PCW_MIO_3_SLEW {slow} \

- CONFIG.PCW_MIO_40_DIRECTION {inout} \

- CONFIG.PCW_MIO_40_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_40_PULLUP {enabled} \

- CONFIG.PCW_MIO_40_SLEW {slow} \

- CONFIG.PCW_MIO_41_DIRECTION {inout} \

- CONFIG.PCW_MIO_41_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_41_PULLUP {enabled} \

- CONFIG.PCW_MIO_41_SLEW {slow} \

- CONFIG.PCW_MIO_42_DIRECTION {inout} \

- CONFIG.PCW_MIO_42_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_42_PULLUP {enabled} \

- CONFIG.PCW_MIO_42_SLEW {slow} \

- CONFIG.PCW_MIO_43_DIRECTION {inout} \

- CONFIG.PCW_MIO_43_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_43_PULLUP {enabled} \

- CONFIG.PCW_MIO_43_SLEW {slow} \

- CONFIG.PCW_MIO_44_DIRECTION {inout} \

- CONFIG.PCW_MIO_44_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_44_PULLUP {enabled} \

- CONFIG.PCW_MIO_44_SLEW {slow} \

- CONFIG.PCW_MIO_45_DIRECTION {inout} \

- CONFIG.PCW_MIO_45_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_45_PULLUP {enabled} \

- CONFIG.PCW_MIO_45_SLEW {slow} \

- CONFIG.PCW_MIO_46_DIRECTION {out} \

- CONFIG.PCW_MIO_46_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_46_PULLUP {enabled} \

- CONFIG.PCW_MIO_46_SLEW {slow} \

- CONFIG.PCW_MIO_47_DIRECTION {in} \

- CONFIG.PCW_MIO_47_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_47_PULLUP {enabled} \

- CONFIG.PCW_MIO_47_SLEW {slow} \

- CONFIG.PCW_MIO_48_DIRECTION {out} \

- CONFIG.PCW_MIO_48_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_48_PULLUP {enabled} \

- CONFIG.PCW_MIO_48_SLEW {slow} \

- CONFIG.PCW_MIO_49_DIRECTION {in} \

- CONFIG.PCW_MIO_49_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_49_PULLUP {enabled} \

- CONFIG.PCW_MIO_49_SLEW {slow} \

- CONFIG.PCW_MIO_4_DIRECTION {inout} \

- CONFIG.PCW_MIO_4_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_4_PULLUP {disabled} \

- CONFIG.PCW_MIO_4_SLEW {slow} \

- CONFIG.PCW_MIO_50_DIRECTION {inout} \

- CONFIG.PCW_MIO_50_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_50_PULLUP {enabled} \

- CONFIG.PCW_MIO_50_SLEW {slow} \

- CONFIG.PCW_MIO_51_DIRECTION {inout} \

- CONFIG.PCW_MIO_51_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_51_PULLUP {enabled} \

- CONFIG.PCW_MIO_51_SLEW {slow} \

- CONFIG.PCW_MIO_52_DIRECTION {out} \

- CONFIG.PCW_MIO_52_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_52_PULLUP {enabled} \

- CONFIG.PCW_MIO_52_SLEW {slow} \

- CONFIG.PCW_MIO_53_DIRECTION {inout} \

- CONFIG.PCW_MIO_53_IOTYPE {LVCMOS 1.8V} \

- CONFIG.PCW_MIO_53_PULLUP {enabled} \

- CONFIG.PCW_MIO_53_SLEW {slow} \

- CONFIG.PCW_MIO_5_DIRECTION {inout} \

- CONFIG.PCW_MIO_5_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_5_PULLUP {disabled} \

- CONFIG.PCW_MIO_5_SLEW {slow} \

- CONFIG.PCW_MIO_6_DIRECTION {out} \

- CONFIG.PCW_MIO_6_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_6_PULLUP {disabled} \

- CONFIG.PCW_MIO_6_SLEW {slow} \

- CONFIG.PCW_MIO_7_DIRECTION {out} \

- CONFIG.PCW_MIO_7_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_7_PULLUP {disabled} \

- CONFIG.PCW_MIO_7_SLEW {slow} \

- CONFIG.PCW_MIO_8_DIRECTION {out} \

- CONFIG.PCW_MIO_8_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_8_PULLUP {disabled} \

- CONFIG.PCW_MIO_8_SLEW {slow} \

- CONFIG.PCW_MIO_9_DIRECTION {inout} \

- CONFIG.PCW_MIO_9_IOTYPE {LVCMOS 3.3V} \

- CONFIG.PCW_MIO_9_PULLUP {enabled} \

- CONFIG.PCW_MIO_9_SLEW {slow} \

- CONFIG.PCW_MIO_TREE_PERIPHERALS {GPIO#Quad SPI Flash#Quad SPI Flash#Quad SPI Flash#Quad SPI Flash#Quad SPI Flash#Quad SPI Flash#GPIO#Quad SPI Flash#GPIO#GPIO#GPIO#I2C 1#I2C 1#I2C 0#I2C 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#Enet 0#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#GPIO#UART 1#UART 1#GPIO#GPIO#Enet 0#Enet 0} \

- CONFIG.PCW_MIO_TREE_SIGNALS {gpio0#qspi0_ss_b#qspi0_io0#qspi0_io1#qspi0_io2#qspi0_io3/HOLD_B#qspi0_sclk#gpio7#qspi_fbclk#gpio9#gpio10#gpio11#scl#sda#scl#sda#tx_clk#txd0#txd1#txd2#txd3#tx_ctl#rx_clk#rxd0#rxd1#rxd2#rxd3#rx_ctl#gpio28#gpio29#gpio30#gpio31#gpio32#gpio33#gpio34#gpio35#gpio36#gpio37#gpio38#gpio39#gpio40#gpio41#gpio42#gpio43#gpio44#gpio45#gpio46#gpio47#tx#rx#gpio50#gpio51#mdc#mdio} \

- CONFIG.PCW_NAND_GRP_D8_ENABLE {0} \

- CONFIG.PCW_NAND_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_NOR_GRP_A25_ENABLE {0} \

- CONFIG.PCW_NOR_GRP_CS0_ENABLE {0} \

- CONFIG.PCW_NOR_GRP_CS1_ENABLE {0} \

- CONFIG.PCW_NOR_GRP_SRAM_CS0_ENABLE {0} \

- CONFIG.PCW_NOR_GRP_SRAM_CS1_ENABLE {0} \

- CONFIG.PCW_NOR_GRP_SRAM_INT_ENABLE {0} \

- CONFIG.PCW_NOR_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_OVERRIDE_BASIC_CLOCK {0} \

- CONFIG.PCW_PACKAGE_DDR_BOARD_DELAY0 {0.221} \

- CONFIG.PCW_PACKAGE_DDR_BOARD_DELAY1 {0.222} \

- CONFIG.PCW_PACKAGE_DDR_BOARD_DELAY2 {0.217} \

- CONFIG.PCW_PACKAGE_DDR_BOARD_DELAY3 {0.244} \

- CONFIG.PCW_PACKAGE_DDR_DQS_TO_CLK_DELAY_0 {-0.050} \

- CONFIG.PCW_PACKAGE_DDR_DQS_TO_CLK_DELAY_1 {-0.044} \

- CONFIG.PCW_PACKAGE_DDR_DQS_TO_CLK_DELAY_2 {-0.035} \

- CONFIG.PCW_PACKAGE_DDR_DQS_TO_CLK_DELAY_3 {-0.100} \

- CONFIG.PCW_PCAP_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_PCAP_PERIPHERAL_DIVISOR0 {5} \

- CONFIG.PCW_PCAP_PERIPHERAL_FREQMHZ {200} \

- CONFIG.PCW_PJTAG_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_PLL_BYPASSMODE_ENABLE {0} \

- CONFIG.PCW_PRESET_BANK0_VOLTAGE {LVCMOS 3.3V} \

- CONFIG.PCW_PRESET_BANK1_VOLTAGE {LVCMOS 1.8V} \

- CONFIG.PCW_QSPI_GRP_FBCLK_ENABLE {1} \

- CONFIG.PCW_QSPI_GRP_FBCLK_IO {MIO 8} \

- CONFIG.PCW_QSPI_GRP_IO1_ENABLE {0} \

- CONFIG.PCW_QSPI_GRP_SINGLE_SS_ENABLE {1} \

- CONFIG.PCW_QSPI_GRP_SINGLE_SS_IO {MIO 1 .. 6} \

- CONFIG.PCW_QSPI_GRP_SS1_ENABLE {0} \

- CONFIG.PCW_QSPI_INTERNAL_HIGHADDRESS {0xFCFFFFFF} \

- CONFIG.PCW_QSPI_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_QSPI_PERIPHERAL_DIVISOR0 {5} \

- CONFIG.PCW_QSPI_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_QSPI_PERIPHERAL_FREQMHZ {200} \

- CONFIG.PCW_QSPI_QSPI_IO {MIO 1 .. 6} \

- CONFIG.PCW_SD0_GRP_CD_ENABLE {0} \

- CONFIG.PCW_SD0_GRP_CD_IO {<Select>} \

- CONFIG.PCW_SD0_GRP_POW_ENABLE {0} \

- CONFIG.PCW_SD0_GRP_WP_ENABLE {0} \

- CONFIG.PCW_SD0_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_SD0_SD0_IO {<Select>} \

- CONFIG.PCW_SDIO_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_SDIO_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_SDIO_PERIPHERAL_FREQMHZ {50} \

- CONFIG.PCW_SDIO_PERIPHERAL_VALID {0} \

- CONFIG.PCW_SINGLE_QSPI_DATA_MODE {x4} \

- CONFIG.PCW_SMC_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_SMC_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_SMC_PERIPHERAL_FREQMHZ {100} \

- CONFIG.PCW_SPI_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_TPIU_PERIPHERAL_CLKSRC {External} \

- CONFIG.PCW_TPIU_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_TPIU_PERIPHERAL_FREQMHZ {200} \

- CONFIG.PCW_UART1_BAUD_RATE {115200} \

- CONFIG.PCW_UART1_GRP_FULL_ENABLE {0} \

- CONFIG.PCW_UART1_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_UART1_UART1_IO {MIO 48 .. 49} \

- CONFIG.PCW_UART_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_UART_PERIPHERAL_DIVISOR0 {10} \

- CONFIG.PCW_UART_PERIPHERAL_FREQMHZ {100} \

- CONFIG.PCW_UART_PERIPHERAL_VALID {1} \

- CONFIG.PCW_UIPARAM_ACT_DDR_FREQ_MHZ {533.333374} \

- CONFIG.PCW_UIPARAM_DDR_ADV_ENABLE {0} \

- CONFIG.PCW_UIPARAM_DDR_AL {0} \

- CONFIG.PCW_UIPARAM_DDR_BANK_ADDR_COUNT {3} \

- CONFIG.PCW_UIPARAM_DDR_BL {8} \

- CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY0 {0.221} \

- CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY1 {0.222} \

- CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY2 {0.217} \

- CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY3 {0.244} \

- CONFIG.PCW_UIPARAM_DDR_BUS_WIDTH {32 Bit} \

- CONFIG.PCW_UIPARAM_DDR_CL {7} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_0_LENGTH_MM {18.8} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_0_PACKAGE_LENGTH {80.4535} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_0_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_1_LENGTH_MM {18.8} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_1_PACKAGE_LENGTH {80.4535} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_1_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_2_LENGTH_MM {18.8} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_2_PACKAGE_LENGTH {80.4535} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_2_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_3_LENGTH_MM {18.8} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_3_PACKAGE_LENGTH {80.4535} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_3_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_CLOCK_STOP_EN {0} \

- CONFIG.PCW_UIPARAM_DDR_COL_ADDR_COUNT {10} \

- CONFIG.PCW_UIPARAM_DDR_CWL {6} \

- CONFIG.PCW_UIPARAM_DDR_DEVICE_CAPACITY {4096 MBits} \

- CONFIG.PCW_UIPARAM_DDR_DQS_0_LENGTH_MM {22.8} \

- CONFIG.PCW_UIPARAM_DDR_DQS_0_PACKAGE_LENGTH {105.056} \

- CONFIG.PCW_UIPARAM_DDR_DQS_0_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQS_1_LENGTH_MM {27.9} \

- CONFIG.PCW_UIPARAM_DDR_DQS_1_PACKAGE_LENGTH {66.904} \

- CONFIG.PCW_UIPARAM_DDR_DQS_1_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQS_2_LENGTH_MM {22.9} \

- CONFIG.PCW_UIPARAM_DDR_DQS_2_PACKAGE_LENGTH {89.1715} \

- CONFIG.PCW_UIPARAM_DDR_DQS_2_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQS_3_LENGTH_MM {29.4} \

- CONFIG.PCW_UIPARAM_DDR_DQS_3_PACKAGE_LENGTH {113.63} \

- CONFIG.PCW_UIPARAM_DDR_DQS_3_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_0 {-0.050} \

- CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_1 {-0.044} \

- CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_2 {-0.035} \

- CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_3 {-0.100} \

- CONFIG.PCW_UIPARAM_DDR_DQ_0_LENGTH_MM {22.8} \

- CONFIG.PCW_UIPARAM_DDR_DQ_0_PACKAGE_LENGTH {98.503} \

- CONFIG.PCW_UIPARAM_DDR_DQ_0_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQ_1_LENGTH_MM {27.9} \

- CONFIG.PCW_UIPARAM_DDR_DQ_1_PACKAGE_LENGTH {68.5855} \

- CONFIG.PCW_UIPARAM_DDR_DQ_1_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQ_2_LENGTH_MM {22.9} \

- CONFIG.PCW_UIPARAM_DDR_DQ_2_PACKAGE_LENGTH {90.295} \

- CONFIG.PCW_UIPARAM_DDR_DQ_2_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DQ_3_LENGTH_MM {29.4} \

- CONFIG.PCW_UIPARAM_DDR_DQ_3_PACKAGE_LENGTH {103.977} \

- CONFIG.PCW_UIPARAM_DDR_DQ_3_PROPOGATION_DELAY {160} \

- CONFIG.PCW_UIPARAM_DDR_DRAM_WIDTH {16 Bits} \

- CONFIG.PCW_UIPARAM_DDR_ECC {Disabled} \

- CONFIG.PCW_UIPARAM_DDR_ENABLE {1} \

- CONFIG.PCW_UIPARAM_DDR_FREQ_MHZ {533.333333} \

- CONFIG.PCW_UIPARAM_DDR_HIGH_TEMP {Normal (0-85)} \

- CONFIG.PCW_UIPARAM_DDR_MEMORY_TYPE {DDR 3 (Low Voltage)} \

- CONFIG.PCW_UIPARAM_DDR_PARTNO {MT41K256M16 RE-125} \

- CONFIG.PCW_UIPARAM_DDR_ROW_ADDR_COUNT {15} \

- CONFIG.PCW_UIPARAM_DDR_SPEED_BIN {DDR3_1066F} \

- CONFIG.PCW_UIPARAM_DDR_TRAIN_DATA_EYE {1} \

- CONFIG.PCW_UIPARAM_DDR_TRAIN_READ_GATE {1} \

- CONFIG.PCW_UIPARAM_DDR_TRAIN_WRITE_LEVEL {1} \

- CONFIG.PCW_UIPARAM_DDR_T_FAW {40.0} \

- CONFIG.PCW_UIPARAM_DDR_T_RAS_MIN {35.0} \

- CONFIG.PCW_UIPARAM_DDR_T_RC {48.75} \

- CONFIG.PCW_UIPARAM_DDR_T_RCD {7} \

- CONFIG.PCW_UIPARAM_DDR_T_RP {7} \

- CONFIG.PCW_UIPARAM_DDR_USE_INTERNAL_VREF {0} \

- CONFIG.PCW_USB0_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_USB0_PERIPHERAL_FREQMHZ {60} \

- CONFIG.PCW_USB0_RESET_ENABLE {1} \

- CONFIG.PCW_USB0_RESET_IO {MIO 46} \

- CONFIG.PCW_USB0_USB0_IO {<Select>} \

- CONFIG.PCW_USB1_RESET_ENABLE {0} \

- CONFIG.PCW_USB_RESET_ENABLE {1} \

- CONFIG.PCW_USB_RESET_POLARITY {Active Low} \

- CONFIG.PCW_USB_RESET_SELECT {<Select>} \

- CONFIG.PCW_USE_AXI_NONSECURE {0} \

- CONFIG.PCW_USE_CROSS_TRIGGER {0} \

- CONFIG.PCW_USE_M_AXI_GP0 {0} \

- ] $processing_system7_0

- # Create interface connections

- connect_bd_intf_net -intf_net processing_system7_0_DDR [get_bd_intf_ports DDR] [get_bd_intf_pins processing_system7_0/DDR]

- connect_bd_intf_net -intf_net processing_system7_0_FIXED_IO [get_bd_intf_ports FIXED_IO] [get_bd_intf_pins processing_system7_0/FIXED_IO]

- connect_bd_intf_net -intf_net processing_system7_0_GPIO_0 [get_bd_intf_ports GPIO_0_0] [get_bd_intf_pins processing_system7_0/GPIO_0]

- # Create port connections

- # Create address segments

- # Perform GUI Layout

- regenerate_bd_layout -layout_string {

- "ActiveEmotionalView":"Default View",

- "Default View_ScaleFactor":"1.0",

- "Default View_TopLeft":"-337,-352",

- "ExpandedHierarchyInLayout":"",

- "guistr":"# # String gsaved with Nlview 7.0r6 2020-01-29 bk=1.5227 VDI=41 GEI=36 GUI=JA:10.0 non-TLS

- # -string -flagsOSRD

- preplace port DDR -pg 1 -lvl 2 -x 430 -y -120 -defaultsOSRD

- preplace port FIXED_IO -pg 1 -lvl 2 -x 430 -y -100 -defaultsOSRD

- preplace port GPIO_0_0 -pg 1 -lvl 2 -x 430 -y -140 -defaultsOSRD

- preplace inst processing_system7_0 -pg 1 -lvl 1 -x 210 -y -100 -defaultsOSRD

- preplace netloc processing_system7_0_GPIO_0 1 1 1 N -140

- preplace netloc processing_system7_0_FIXED_IO 1 1 1 NJ -100

- preplace netloc processing_system7_0_DDR 1 1 1 NJ -120

- levelinfo -pg 1 0 210 430

- pagesize -pg 1 -db -bbox -sgen 0 -220 550 200

- "

- }

- # Restore current instance

- current_bd_instance $oldCurInst

- validate_bd_design

- save_bd_design

- close_bd_design $design_name

- }

- cr_bd_design_1 ""

INFO: [BD::TCL 103-2010] Currently there is no design <design_1> in project, so creating one...

Wrote : <C:\AimaginProjects\Zybo\Hardware_Z7000\i2c_demo\project_1\project_1.srcs\sources_1\bd\design_1\design_1.bd>

create_bd_design: Time (s): cpu = 00:00:04 ; elapsed = 00:00:07 . Memory (MB): peak = 1119.531 ; gain = 0.000

INFO: [BD::TCL 103-2011] Checking if the following IPs exist in the project's IP catalog:

xilinx.com:ip:processing_system7:5.5 .

CRITICAL WARNING: [PSU-1] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_0 has negative value -0.050 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-2] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_1 has negative value -0.044 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-3] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_2 has negative value -0.035 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-4] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_3 has negative value -0.100 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-1] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_0 has negative value -0.050 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-2] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_1 has negative value -0.044 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-3] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_2 has negative value -0.035 . PS DDR interfaces might fail when entering negative DQS skew values.

CRITICAL WARNING: [PSU-4] Parameter : PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_3 has negative value -0.100 . PS DDR interfaces might fail when entering negative DQS skew values.

Wrote : <C:\AimaginProjects\Zybo\Hardware_Z7000\i2c_demo\project_1\project_1.srcs\sources_1\bd\design_1\design_1.bd>

Wrote : <C:/AimaginProjects/Zybo/Hardware_Z7000/i2c_demo/project_1/project_1.srcs/sources_1/bd/design_1/ui/bd_1f5defd0.ui> - set_property REGISTERED_WITH_MANAGER "1" [get_files design_1.bd ]

- set_property SYNTH_CHECKPOINT_MODE "Hierarchical" [get_files design_1.bd ]

- if { [get_property IS_LOCKED [ get_files -norecurse design_1.bd] ] == 1 } {

- import_files -fileset sources_1 [file normalize "${origin_dir}/project_1/project_1.gen/sources_1/bd/design_1/hdl/design_1_wrapper.vhd" ]

- } else {

- set wrapper_path [make_wrapper -fileset sources_1 -files [ get_files -norecurse design_1.bd] -top]

- add_files -norecurse -fileset sources_1 $wrapper_path

- }

INFO: [BD 41-1662] The design 'design_1.bd' is already validated. Therefore parameter propagation will not be re-run.

VHDL Output written to : c:/AimaginProjects/Zybo/Hardware_Z7000/i2c_demo/project_1/project_1.gen/sources_1/bd/design_1/synth/design_1.vhd

VHDL Output written to : c:/AimaginProjects/Zybo/Hardware_Z7000/i2c_demo/project_1/project_1.gen/sources_1/bd/design_1/sim/design_1.vhd

VHDL Output written to : c:/AimaginProjects/Zybo/Hardware_Z7000/i2c_demo/project_1/project_1.gen/sources_1/bd/design_1/hdl/design_1_wrapper.vhd

make_wrapper: Time (s): cpu = 00:00:01 ; elapsed = 00:00:07 . Memory (MB): peak = 1420.555 ; gain = 126.723 - if {[string equal [get_runs -quiet synth_1] ""]} {

- create_run -name synth_1 -part xc7z020clg400-1 -flow {Vivado Synthesis 2020} -strategy "Vivado Synthesis Defaults" -report_strategy {No Reports} -constrset constrs_1

- } else {

- set_property strategy "Vivado Synthesis Defaults" [get_runs synth_1]

- set_property flow "Vivado Synthesis 2020" [get_runs synth_1]

- }

- set obj [get_runs synth_1]

- set_property set_report_strategy_name 1 $obj

- set_property report_strategy {Vivado Synthesis Default Reports} $obj

- set_property set_report_strategy_name 0 $obj

- if { [ string equal [get_report_configs -of_objects [get_runs synth_1] synth_1_synth_report_utilization_0] "" ] } {

- create_report_config -report_name synth_1_synth_report_utilization_0 -report_type report_utilization:1.0 -steps synth_design -runs synth_1

- }

- set obj [get_report_configs -of_objects [get_runs synth_1] synth_1_synth_report_utilization_0]

- if { $obj != "" } {

- }

- set obj [get_runs synth_1]

- set_property -name "strategy" -value "Vivado Synthesis Defaults" -objects $obj

- current_run -synthesis [get_runs synth_1]

- if {[string equal [get_runs -quiet impl_1] ""]} {

- create_run -name impl_1 -part xc7z020clg400-1 -flow {Vivado Implementation 2020} -strategy "Vivado Implementation Defaults" -report_strategy {No Reports} -constrset constrs_1 -parent_run synth_1

- } else {

- set_property strategy "Vivado Implementation Defaults" [get_runs impl_1]

- set_property flow "Vivado Implementation 2020" [get_runs impl_1]

- }

- set obj [get_runs impl_1]

- set_property set_report_strategy_name 1 $obj

- set_property report_strategy {Vivado Implementation Default Reports} $obj

- set_property set_report_strategy_name 0 $obj

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_init_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_init_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps init_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_init_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_opt_report_drc_0] "" ] } {

- create_report_config -report_name impl_1_opt_report_drc_0 -report_type report_drc:1.0 -steps opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_opt_report_drc_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_opt_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_opt_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_opt_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_power_opt_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_power_opt_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps power_opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_power_opt_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_io_0] "" ] } {

- create_report_config -report_name impl_1_place_report_io_0 -report_type report_io:1.0 -steps place_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_io_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_utilization_0] "" ] } {

- create_report_config -report_name impl_1_place_report_utilization_0 -report_type report_utilization:1.0 -steps place_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_utilization_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_control_sets_0] "" ] } {

- create_report_config -report_name impl_1_place_report_control_sets_0 -report_type report_control_sets:1.0 -steps place_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_control_sets_0]

- if { $obj != "" } {

- set_property -name "options.verbose" -value "1" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_incremental_reuse_0] "" ] } {

- create_report_config -report_name impl_1_place_report_incremental_reuse_0 -report_type report_incremental_reuse:1.0 -steps place_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_incremental_reuse_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_incremental_reuse_1] "" ] } {

- create_report_config -report_name impl_1_place_report_incremental_reuse_1 -report_type report_incremental_reuse:1.0 -steps place_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_incremental_reuse_1]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_place_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps place_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_place_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_post_place_power_opt_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_post_place_power_opt_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps post_place_power_opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_post_place_power_opt_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_phys_opt_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_phys_opt_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps phys_opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_phys_opt_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "is_enabled" -value "0" -objects $obj

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_drc_0] "" ] } {

- create_report_config -report_name impl_1_route_report_drc_0 -report_type report_drc:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_drc_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_methodology_0] "" ] } {

- create_report_config -report_name impl_1_route_report_methodology_0 -report_type report_methodology:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_methodology_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_power_0] "" ] } {

- create_report_config -report_name impl_1_route_report_power_0 -report_type report_power:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_power_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_route_status_0] "" ] } {

- create_report_config -report_name impl_1_route_report_route_status_0 -report_type report_route_status:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_route_status_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_route_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "options.max_paths" -value "10" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_incremental_reuse_0] "" ] } {

- create_report_config -report_name impl_1_route_report_incremental_reuse_0 -report_type report_incremental_reuse:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_incremental_reuse_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_clock_utilization_0] "" ] } {

- create_report_config -report_name impl_1_route_report_clock_utilization_0 -report_type report_clock_utilization:1.0 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_clock_utilization_0]

- if { $obj != "" } {

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_bus_skew_0] "" ] } {

- create_report_config -report_name impl_1_route_report_bus_skew_0 -report_type report_bus_skew:1.1 -steps route_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_route_report_bus_skew_0]

- if { $obj != "" } {

- set_property -name "options.warn_on_violation" -value "1" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_post_route_phys_opt_report_timing_summary_0] "" ] } {

- create_report_config -report_name impl_1_post_route_phys_opt_report_timing_summary_0 -report_type report_timing_summary:1.0 -steps post_route_phys_opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_post_route_phys_opt_report_timing_summary_0]

- if { $obj != "" } {

- set_property -name "options.max_paths" -value "10" -objects $obj

- set_property -name "options.warn_on_violation" -value "1" -objects $obj

- }

- if { [ string equal [get_report_configs -of_objects [get_runs impl_1] impl_1_post_route_phys_opt_report_bus_skew_0] "" ] } {

- create_report_config -report_name impl_1_post_route_phys_opt_report_bus_skew_0 -report_type report_bus_skew:1.1 -steps post_route_phys_opt_design -runs impl_1

- }

- set obj [get_report_configs -of_objects [get_runs impl_1] impl_1_post_route_phys_opt_report_bus_skew_0]

- if { $obj != "" } {

- set_property -name "options.warn_on_violation" -value "1" -objects $obj

- }

- set obj [get_runs impl_1]

- set_property -name "strategy" -value "Vivado Implementation Defaults" -objects $obj

- set_property -name "steps.write_bitstream.args.readback_file" -value "0" -objects $obj

- set_property -name "steps.write_bitstream.args.verbose" -value "0" -objects $obj

- current_run -implementation [get_runs impl_1]

- puts "INFO: Project created:${_xil_proj_name_}"

INFO: Project created:project_1 - if {[string equal [get_dashboard_gadgets [ list "drc_1" ] ] ""]} {

- create_dashboard_gadget -name {drc_1} -type drc

- }

- set obj [get_dashboard_gadgets [ list "drc_1" ] ]

- set_property -name "reports" -value "impl_1#impl_1_route_report_drc_0" -objects $obj

- if {[string equal [get_dashboard_gadgets [ list "methodology_1" ] ] ""]} {

- create_dashboard_gadget -name {methodology_1} -type methodology

- }

- set obj [get_dashboard_gadgets [ list "methodology_1" ] ]

- set_property -name "reports" -value "impl_1#impl_1_route_report_methodology_0" -objects $obj

- if {[string equal [get_dashboard_gadgets [ list "power_1" ] ] ""]} {

- create_dashboard_gadget -name {power_1} -type power

- }

- set obj [get_dashboard_gadgets [ list "power_1" ] ]

- set_property -name "reports" -value "impl_1#impl_1_route_report_power_0" -objects $obj

- if {[string equal [get_dashboard_gadgets [ list "timing_1" ] ] ""]} {

- create_dashboard_gadget -name {timing_1} -type timing

- }

- set obj [get_dashboard_gadgets [ list "timing_1" ] ]

- set_property -name "reports" -value "impl_1#impl_1_route_report_timing_summary_0" -objects $obj

- if {[string equal [get_dashboard_gadgets [ list "utilization_1" ] ] ""]} {

- create_dashboard_gadget -name {utilization_1} -type utilization

- }

- set obj [get_dashboard_gadgets [ list "utilization_1" ] ]

- set_property -name "reports" -value "synth_1#synth_1_synth_report_utilization_0" -objects $obj

- set_property -name "run.step" -value "synth_design" -objects $obj

- set_property -name "run.type" -value "synthesis" -objects $obj

- if {[string equal [get_dashboard_gadgets [ list "utilization_2" ] ] ""]} {

- create_dashboard_gadget -name {utilization_2} -type utilization

- }

- set obj [get_dashboard_gadgets [ list "utilization_2" ] ]

- set_property -name "reports" -value "impl_1#impl_1_place_report_utilization_0" -objects $obj

- move_dashboard_gadget -name {utilization_1} -row 0 -col 0

- move_dashboard_gadget -name {power_1} -row 1 -col 0

- move_dashboard_gadget -name {drc_1} -row 2 -col 0

- move_dashboard_gadget -name {timing_1} -row 0 -col 1

- move_dashboard_gadget -name {utilization_2} -row 1 -col 1

- move_dashboard_gadget -name {methodology_1} -row 2 -col 1

update_compile_order -fileset sources_1

RE: Cannot build hardware for i2c_demo

-

Added by Shawn Sebastian Pulle (ฌอน) about 3 years ago

RE: Cannot build hardware for i2c_demo

-

Added by Shawn Sebastian Pulle (ฌอน) about 3 years ago

Hi Johan,

Thank you for the valuable feedback.

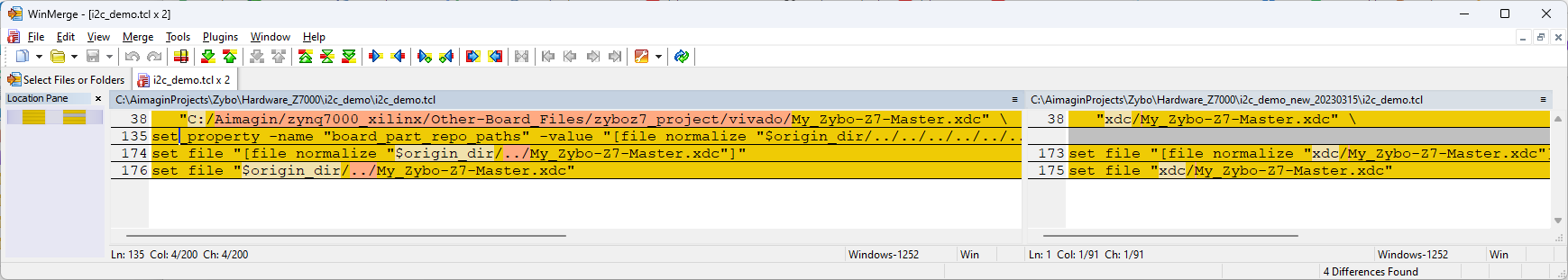

The root cause of this issue is absolute path definitions instead of relative file path definitions inside the tcl file.

Please replace your tcl file located at ".../demo/i2c_demo/hardware_design/vivado_tcl" folder with the attached file and update us with your findings.

| i2c_demo.rar | i2c_demo.rar | 8.14 KB |

RE: Cannot build hardware for i2c_demo

-

Added by Johan Henning about 3 years ago

RE: Cannot build hardware for i2c_demo

-

Added by Johan Henning about 3 years ago

Hello Shawn,

Thanks for the updated .tcl file, this one works fine.

Besides the 8 critical warnings (which do not harm according to the link you've sent me) there is another warning: [IP_Flow 19-474] Invalid Parameter 'Component_Name'. It would be nice to solve that as wel in the future.

Another remark: the created project is called project_1. In case of other hardware projects (for example the adc_demo) the project is called adc_demo (which I like). In case of the gpio_demo the project is called zynq7000_gpio_demo. I prefer gpio_demo to be consistent.

Last remark (for this issue:-) ): It would be very nice if there was only one hardware configuration (.tcl / .xdc) that works for all demo's (I put that whish in the suggestions forum some time ago). That makes maintenance of the hardware much easier. And also combining partial models form the various demo's.

Regards!

johan.

Differences between original and new .tcl file:

RE: Cannot build hardware for i2c_demo

-

Added by Shawn Sebastian Pulle (ฌอน) about 3 years ago

RE: Cannot build hardware for i2c_demo

-

Added by Shawn Sebastian Pulle (ฌอน) about 3 years ago

Hi Johan,

Thank you for the feedback.

1. Regarding warning: [IP_Flow 19-474] Invalid Parameter 'Component_Name'., we are unable to recreate this error from our end. Would it be possible to attach the full log so we can have an understanding at which point the warning is being thrown?

2. We will try to implement a consistent naming scheme for the projects created via tcl files in our future releases.

3. We are aware of the need and appeal of a hardware reference file that works with all of the demos. We will update you further on this matter on the feature request when we have come to a decision.

Best Regards,

Shawn

RE: Cannot build hardware for i2c_demo

-

Added by Johan Henning about 3 years ago

RE: Cannot build hardware for i2c_demo

-

Added by Johan Henning about 3 years ago

Hello Shawn,

Interestingly I did not get the warning after rebuilding the hardware myself. It has solved itself somehow :-)

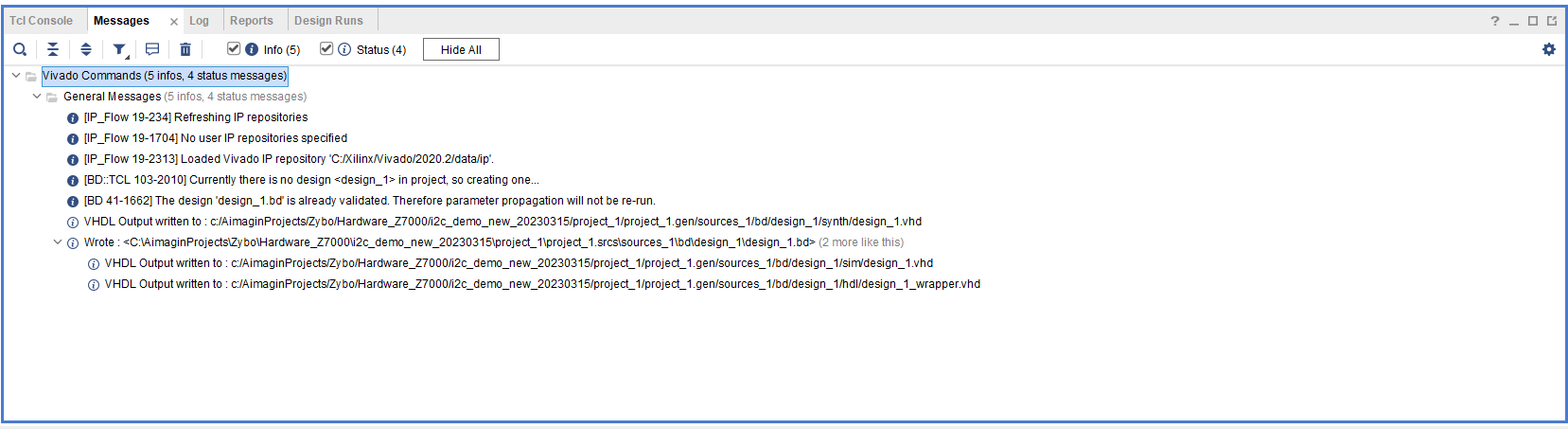

Below my logfile and the status messages.

Regards,

johan.

.

- proc checkRequiredFiles { origin_dir} {

- set status true

- set files [list \

- "xdc/My_Zybo-Z7-Master.xdc" \

- ]

- foreach ifile $files {

- if { ![file isfile $ifile] } {

- puts " Could not find remote file $ifile "

- set status false

- }

- }

- return $status

- }

- set origin_dir "."

- if { [info exists ::origin_dir_loc] } {

- set origin_dir $::origin_dir_loc

- }

- set xil_proj_name "project_1"

- if { [info exists ::user_project_name] } {

- set xil_proj_name $::user_project_name

- }

- variable script_file

- set script_file "i2c_demo.tcl"

- proc print_help {} {

- variable script_file

- puts "\nDescription:"

- puts "Recreate a Vivado project from this script. The created project will be"

- puts "functionally equivalent to the original project for which this script was"

- puts "generated. The script contains commands for creating a project, filesets,"

- puts "runs, adding/importing sources and setting properties on various objects.\n"

- puts "Syntax:"

- puts "$script_file"

- puts "$script_file -tclargs \[--origin_dir <path>\]"

- puts "$script_file -tclargs \[--project_name <name>\]"

- puts "$script_file -tclargs \[--help\]\n"

- puts "Usage:"

- puts "Name Description"

- puts "-------------------------------------------------------------------------"

- puts "\[--origin_dir <path>\] Determine source file paths wrt this path. Default"

- puts " origin_dir path value is \".\", otherwise, the value"

- puts " that was set with the \"-paths_relative_to\" switch"

- puts " when this script was generated.\n"

- puts "\[--project_name <name>\] Create project with the specified name. Default"

- puts " name is the name of the project from where this"

- puts " script was generated.\n"

- puts "\[--help\] Print help information for this script"

- puts "-------------------------------------------------------------------------\n"

- exit 0

- }

- if { $::argc > 0 } {

- for {set i 0} {$i < $::argc} {incr i} {

- set option [string trim [lindex $::argv $i]]

- switch

regexp -$option { - "--origin_dir" { incr i; set origin_dir [lindex $::argv $i] }

- "--project_name" { incr i; set xil_proj_name [lindex $::argv $i] }

- "--help" { print_help }

- default {

- if { [regexp {^-} $option] } {

- puts "ERROR: Unknown option '$option' specified, please type '$script_file -tclargs --help' for usage info.\n"

- return 1

- }

- }

- }

- }

- }

- set orig_proj_dir "[file normalize "$origin_dir/project_1"]"

- set validate_required 0

- if { $validate_required } {

- if { [checkRequiredFiles $origin_dir] } {

- puts "Tcl file $script_file is valid. All files required for project creation is accesable. "

- } else {

- puts "Tcl file $script_file is not valid. Not all files required for project creation is accesable. "

- return

- }

- }

- create_project ${_xil_proj_name_} ./${_xil_proj_name_} -part xc7z020clg400-1

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'C:/Xilinx/Vivado/2020.2/data/ip'.

create_project: Time (s): cpu = 00:00:04 ; elapsed = 00:00:07 . Memory (MB): peak = 1115.910 ; gain = 0.000 - set proj_dir [get_property directory [current_project]]

- set obj [current_project]

- set_property -name "board_part" -value "digilentinc.com:zybo-z7-20:part0:1.0" -objects $obj

- set_property -name "default_lib" -value "xil_defaultlib" -objects $obj

- set_property -name "enable_vhdl_2008" -value "1" -objects $obj

- set_property -name "ip_cache_permissions" -value "read write" -objects $obj

- set_property -name "ip_output_repo" -value "$proj_dir/${_xil_proj_name_}.cache/ip" -objects $obj

- set_property -name "mem.enable_memory_map_generation" -value "1" -objects $obj

- set_property -name "platform.board_id" -value "zybo-z7-20" -objects $obj

- set_property -name "sim.central_dir" -value "$proj_dir/${_xil_proj_name_}.ip_user_files" -objects $obj

- set_property -name "sim.ip.auto_export_scripts" -value "1" -objects $obj

- set_property -name "simulator_language" -value "Mixed" -objects $obj

- set_property -name "target_language" -value "VHDL" -objects $obj

- if {[string equal [get_filesets -quiet sources_1] ""]} {

- create_fileset -srcset sources_1

- }

- set obj [get_filesets sources_1]

- set obj [get_filesets sources_1]

- set_property -name "top" -value "design_1_wrapper" -objects $obj

- if {[string equal [get_filesets -quiet constrs_1] ""]} {

- create_fileset -constrset constrs_1

- }

- set obj [get_filesets constrs_1]

- set file "[file normalize "xdc/My_Zybo-Z7-Master.xdc"]"

- set file_added [add_files -norecurse -fileset $obj [list $file]]

- set file "xdc/My_Zybo-Z7-Master.xdc"

- set file [file normalize $file]

- set file_obj [get_files -of_objects [get_filesets constrs_1] [list "*$file"]]

- set_property -name "file_type" -value "XDC" -objects $file_obj

- set obj [get_filesets constrs_1]

- if {[string equal [get_filesets -quiet sim_1] ""]} {

- create_fileset -simset sim_1

- }

- set obj [get_filesets sim_1]

- set obj [get_filesets sim_1]

- set_property -name "hbs.configure_design_for_hier_access" -value "1" -objects $obj

- set_property -name "top" -value "design_1_wrapper" -objects $obj

- set_property -name "top_lib" -value "xil_defaultlib" -objects $obj

- set obj [get_filesets utils_1]

- set obj [get_filesets utils_1]

- proc cr_bd_design_1 { parentCell } {

- # CHANGE DESIGN NAME HERE

- set design_name design_1

- common::send_gid_msg -ssname BD::TCL -id 2010 -severity "INFO" "Currently there is no design <$design_name> in project, so creating one..."

- create_bd_design $design_name

- set bCheckIPsPassed 1

- ##################################################################

- # CHECK IPs

- ##################################################################

- set bCheckIPs 1

- if { $bCheckIPs == 1 } {

- set list_check_ips "\

- xilinx.com:ip:processing_system7:5.5\

- "

- set list_ips_missing ""

- common::send_gid_msg -ssname BD::TCL -id 2011 -severity "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."

- foreach ip_vlnv $list_check_ips {

- set ip_obj [get_ipdefs -all $ip_vlnv]

- if { $ip_obj eq "" } {

- lappend list_ips_missing $ip_vlnv

- }

- }

- if { $list_ips_missing ne "" } {

- catch {common::send_gid_msg -ssname BD::TCL -id 2012 -severity "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP to the project." }

- set bCheckIPsPassed 0

- }

- }

- if { $bCheckIPsPassed != 1 } {

- common::send_gid_msg -ssname BD::TCL -id 2023 -severity "WARNING" "Will not continue with creation of design due to the error(s) above."

- return 3

- }

- variable script_folder

- if { $parentCell eq "" } {

- set parentCell [get_bd_cells /]

- }

- # Get object for parentCell

- set parentObj [get_bd_cells $parentCell]

- if { $parentObj == "" } {

- catch {common::send_gid_msg -ssname BD::TCL -id 2090 -severity "ERROR" "Unable to find parent cell <$parentCell>!"}

- return

- }

- # Make sure parentObj is hier blk

- set parentType [get_property TYPE $parentObj]

- if { $parentType ne "hier" } {

- catch {common::send_gid_msg -ssname BD::TCL -id 2091 -severity "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

- return

- }

- # Save current instance; Restore later

- set oldCurInst [current_bd_instance .]

- # Set parent object as current

- current_bd_instance $parentObj

- # Create interface ports

- set DDR [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:ddrx_rtl:1.0 DDR ]

- set FIXED_IO [ create_bd_intf_port -mode Master -vlnv xilinx.com:display_processing_system7:fixedio_rtl:1.0 FIXED_IO ]

- set GPIO_0_0 [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:gpio_rtl:1.0 GPIO_0_0 ]

- # Create ports

- # Create instance: processing_system7_0, and set properties

- set processing_system7_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:processing_system7:5.5 processing_system7_0 ]

- set_property -dict [ list \

- CONFIG.PCW_ACT_APU_PERIPHERAL_FREQMHZ {666.666687} \

- CONFIG.PCW_ACT_CAN_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_DCI_PERIPHERAL_FREQMHZ {10.158730} \

- CONFIG.PCW_ACT_ENET0_PERIPHERAL_FREQMHZ {125.000000} \

- CONFIG.PCW_ACT_ENET1_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_FPGA0_PERIPHERAL_FREQMHZ {50.000000} \

- CONFIG.PCW_ACT_FPGA1_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_FPGA2_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_FPGA3_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_PCAP_PERIPHERAL_FREQMHZ {200.000000} \

- CONFIG.PCW_ACT_QSPI_PERIPHERAL_FREQMHZ {200.000000} \

- CONFIG.PCW_ACT_SDIO_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_SMC_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_SPI_PERIPHERAL_FREQMHZ {10.000000} \

- CONFIG.PCW_ACT_TPIU_PERIPHERAL_FREQMHZ {200.000000} \

- CONFIG.PCW_ACT_TTC0_CLK0_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC0_CLK1_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC0_CLK2_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC1_CLK0_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC1_CLK1_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_TTC1_CLK2_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_ACT_UART_PERIPHERAL_FREQMHZ {100.000000} \

- CONFIG.PCW_ACT_WDT_PERIPHERAL_FREQMHZ {111.111115} \

- CONFIG.PCW_APU_CLK_RATIO_ENABLE {6:2:1} \

- CONFIG.PCW_APU_PERIPHERAL_FREQMHZ {667} \

- CONFIG.PCW_ARMPLL_CTRL_FBDIV {40} \

- CONFIG.PCW_CAN_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_CAN_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_CLK0_FREQ {50000000} \

- CONFIG.PCW_CLK1_FREQ {10000000} \

- CONFIG.PCW_CLK2_FREQ {10000000} \

- CONFIG.PCW_CLK3_FREQ {10000000} \

- CONFIG.PCW_CPU_CPU_6X4X_MAX_RANGE {667} \

- CONFIG.PCW_CPU_CPU_PLL_FREQMHZ {1333.333} \

- CONFIG.PCW_CPU_PERIPHERAL_CLKSRC {ARM PLL} \

- CONFIG.PCW_CPU_PERIPHERAL_DIVISOR0 {2} \

- CONFIG.PCW_CRYSTAL_PERIPHERAL_FREQMHZ {33.333333} \

- CONFIG.PCW_DCI_PERIPHERAL_CLKSRC {DDR PLL} \

- CONFIG.PCW_DCI_PERIPHERAL_DIVISOR0 {15} \

- CONFIG.PCW_DCI_PERIPHERAL_DIVISOR1 {7} \

- CONFIG.PCW_DCI_PERIPHERAL_FREQMHZ {10.159} \

- CONFIG.PCW_DDRPLL_CTRL_FBDIV {32} \

- CONFIG.PCW_DDR_DDR_PLL_FREQMHZ {1066.667} \

- CONFIG.PCW_DDR_HPRLPR_QUEUE_PARTITION {HPR/LPR} \

- CONFIG.PCW_DDR_HPR_TO_CRITICAL_PRIORITY_LEVEL {15} \

- CONFIG.PCW_DDR_LPR_TO_CRITICAL_PRIORITY_LEVEL {2} \

- CONFIG.PCW_DDR_PERIPHERAL_CLKSRC {DDR PLL} \

- CONFIG.PCW_DDR_PERIPHERAL_DIVISOR0 {2} \

- CONFIG.PCW_DDR_PORT0_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_PORT1_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_PORT2_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_PORT3_HPR_ENABLE {0} \

- CONFIG.PCW_DDR_RAM_HIGHADDR {0x3FFFFFFF} \

- CONFIG.PCW_DDR_WRITE_TO_CRITICAL_PRIORITY_LEVEL {2} \

- CONFIG.PCW_ENET0_ENET0_IO {MIO 16 .. 27} \

- CONFIG.PCW_ENET0_GRP_MDIO_ENABLE {1} \

- CONFIG.PCW_ENET0_GRP_MDIO_IO {MIO 52 .. 53} \

- CONFIG.PCW_ENET0_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_ENET0_PERIPHERAL_DIVISOR0 {8} \

- CONFIG.PCW_ENET0_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_ENET0_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_ENET0_PERIPHERAL_FREQMHZ {1000 Mbps} \

- CONFIG.PCW_ENET0_RESET_ENABLE {0} \

- CONFIG.PCW_ENET1_GRP_MDIO_ENABLE {0} \

- CONFIG.PCW_ENET1_PERIPHERAL_CLKSRC {IO PLL} \

- CONFIG.PCW_ENET1_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_ENET1_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_ENET1_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_ENET1_PERIPHERAL_FREQMHZ {1000 Mbps} \

- CONFIG.PCW_ENET1_RESET_ENABLE {0} \

- CONFIG.PCW_ENET_RESET_ENABLE {1} \

- CONFIG.PCW_ENET_RESET_POLARITY {Active Low} \

- CONFIG.PCW_ENET_RESET_SELECT {Share reset pin} \

- CONFIG.PCW_EN_4K_TIMER {0} \

- CONFIG.PCW_EN_EMIO_ENET0 {0} \

- CONFIG.PCW_EN_EMIO_GPIO {1} \

- CONFIG.PCW_EN_EMIO_I2C0 {0} \

- CONFIG.PCW_EN_EMIO_I2C1 {0} \

- CONFIG.PCW_EN_ENET0 {1} \

- CONFIG.PCW_EN_GPIO {1} \

- CONFIG.PCW_EN_I2C0 {1} \

- CONFIG.PCW_EN_I2C1 {1} \

- CONFIG.PCW_EN_QSPI {1} \

- CONFIG.PCW_EN_SDIO0 {0} \

- CONFIG.PCW_EN_UART1 {1} \

- CONFIG.PCW_EN_USB0 {0} \

- CONFIG.PCW_FCLK0_PERIPHERAL_DIVISOR0 {5} \

- CONFIG.PCW_FCLK0_PERIPHERAL_DIVISOR1 {4} \

- CONFIG.PCW_FCLK1_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_FCLK1_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_FCLK2_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_FCLK2_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_FCLK3_PERIPHERAL_DIVISOR0 {1} \

- CONFIG.PCW_FCLK3_PERIPHERAL_DIVISOR1 {1} \

- CONFIG.PCW_FPGA_FCLK0_ENABLE {1} \

- CONFIG.PCW_FPGA_FCLK1_ENABLE {0} \

- CONFIG.PCW_FPGA_FCLK2_ENABLE {0} \

- CONFIG.PCW_FPGA_FCLK3_ENABLE {0} \

- CONFIG.PCW_GPIO_EMIO_GPIO_ENABLE {1} \

- CONFIG.PCW_GPIO_EMIO_GPIO_IO {26} \

- CONFIG.PCW_GPIO_EMIO_GPIO_WIDTH {26} \

- CONFIG.PCW_GPIO_MIO_GPIO_ENABLE {1} \

- CONFIG.PCW_GPIO_MIO_GPIO_IO {MIO} \

- CONFIG.PCW_GPIO_PERIPHERAL_ENABLE {0} \

- CONFIG.PCW_I2C0_GRP_INT_ENABLE {1} \

- CONFIG.PCW_I2C0_GRP_INT_IO {EMIO} \

- CONFIG.PCW_I2C0_I2C0_IO {MIO 14 .. 15} \

- CONFIG.PCW_I2C0_PERIPHERAL_ENABLE {1} \

- CONFIG.PCW_I2C0_RESET_ENABLE {0} \